Research Lab

The Cloud lab offers a flexible facility for experimenting innovative solutions related with distributed, decentralized and heterogeneous cloud infrastructures. In particular, the lab is currently used for testing our assets (FogAtlas and NetStratos) focused on workload and network orchestration and for playing with some leading cloud technologies (mainly OpenStack, Docker and Kubernetes) and exercising their experimental features.

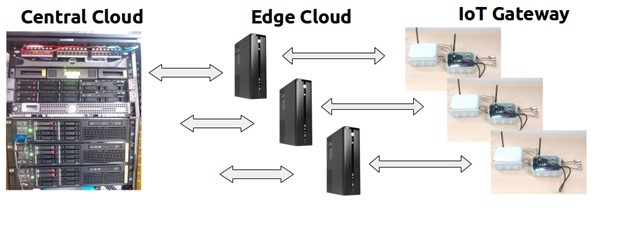

The following picture gives a visual representation of the Cloud Lab.

The Central Cloud runs on dedicated servers and offers IaaS services implemented using the OpenStack platform. The OpenStack environment, configured for High Availability (HA), is composed by 3 Controller nodes and 6 Compute nodes. The controller nodes are Dell PowerEdge R715 whereas the compute nodes are Dell PowerEdge R210 II offering a total of 300 GB RAM, 46TB HD and 128 Cores. The infrastructure is maintained and operated through Ansible and MAAS following the Infrastructure as Code paradigm.

As far as Fog/Edge Cloud and IoT Gateway are concerned, the infrastructure is based on three different kinds of hardware described here under and ordered in terms of their computational capacity:

· mini-itx form factor motherboard with different types of CPU: Intel Xeon E3-1226, Intel Core i7-4790S, Intel Avoton C2750. All of them are equipped with multiple Ethernet network cards, 16GB RAM and 480GB SSD (Fog nodes);

· pcengine apu2c4 AMD GX-412TC CPU with 4 GB DRAM and 16GB SSD (mini-Fog nodes);

· RaspberryPi version 3 device with 1.2 GHz 64-bit quad-core ARM Cortex-A53 CPU, 1GB RAM, 16GB SD card storage, WiFi/BLE/Ethernet default connectivity (Iot Gateways).

The CloudLab is connected, by means of the Divine facility, to an SDN-enabled backbone composed by 3 x 100G Wedge Switches Edge Core (Wedge100BF-32X, 32 port 100G QSFP28 switch, Barefoot Tofino 3.2 Tbps, Intel Broadwell DE CPU, dual AC PSU, port-to-power airflow) located across the city of Trento (and connected by means of 10Gbit/s optical fiber) that allow deep programmability of the data plane by means of the P4 programming language.